**Enabling Energy Efficient Solutions**

www.onsemi.com

#### **ON Semiconductor®**

# **LDO Thermal Calculations**

# **Abstract**

Low Dropout Regulators in present is the cheapest solution for precise voltage source with a few external components. However, the main disadvantage is loss conversion producing significant heat. Therefore proper thermal design is a key for good LDO performance in real applications.

# Agenda

- Thermal parameters standards, terminology and definitions

- Suitable packages for good thermal performance

- Thermal Calculators for LDOs

- Thermal Simulations Used in Silicon Design Phase

# Thermal Parameters Standards, Terminology and Definitions

# **Standards**

- JEDEC specifications:

- Find information related to θ and Ψ parameters definitions and other useful information at website: <u>www.jedec.org</u> in "General Folder" click on "Free Standards" and in "Search by document number:" text field write "JESD51"

- Glossary of Thermal Measurement Terms and Definitions (JESD51-13)

## **Thermal to Electrical Analogy Used**

#### **Electrical**

Voltage (V) Current (A) Resistance (Ω)

Dissipated Power (W)

Thermal Resistance (°C/W)

Thermal

$$I_{R_{XY}} = \frac{V_{XY}}{R_{XY}}$$

$$P_D = \frac{T_X - T_Y}{\theta_{XY}}$$

# θ (Theta) - Thermal Resistance

- $\theta_{xy}$  Thermal Resistance between X and Y points specifies:

- The amount of heat that flows from point X to point Y if the temperatures at X and Y points are known (connected by the thermal resistance). The path the heat flows is known and it is completely determined by the resistance.

- In general

In general:

$$P_D = \frac{T_X - T_Y}{\theta_{XY}}$$

Examples:  $P_D = \frac{T_{J \max} - T_A}{\theta_{JA}}$

$\left(\mathbf{W} = \frac{^{\circ}\mathbf{C}}{^{\circ}\mathbf{C}/\mathbf{W}}\right)$

Calculation of Power Dissipation for given Maximum Junction Temperature and Ambient Temperature. Thermal Resistance is specified for particular application conditions.

The temperature at point X if the temperature at point Y and the amount of heat are known. The path the heat flows is known and it is completely determined by the resistance.

In general:  $T_X = \theta_{XY} \cdot P_D + T_Y$ **Examples:**  $T_I = \theta_{IC} \cdot P_D + T_C$

$$\left( \ ^{\circ}C = \ ^{\circ}C/W \cdot W + \ ^{\circ}C \right)$$

Calculation of Junction Temperature for given Power Dissipation and Case Temperature (i.e. Tab temperature for D2PAK). Thermal Resistance is specified for particular package. (Important: almost all heat flows through the Tab)

# $\Psi$ (Psi) - Thermal Characterization Parameter

- $\Psi_{\text{XY}}$  Thermal Characterization Parameter between X and Y points specifies:

- The temperature difference between point X to point Y if the total heat is known. The heat flowing along the specific path point X to point Y is NOT known.

- This parameter typically serves for estimation of Junction temperature (T<sub>J</sub>) at known total dissipated power (P<sub>D</sub>) inside the package when a temperature is measured at package perimeter (Lead, Exposed Pad, Board, etc.)

In general:

$$T_X = \Psi_{XY} \cdot P_D + T_Y \quad (\circ \mathbf{C} = \circ \mathbf{C}/\mathbf{W} \cdot \mathbf{W} + \circ \mathbf{C})$$

Examples:

$$T_J = \Psi_{JLn} \cdot P_D + T_{Ln}$$

$T_J = \Psi_{JB} \cdot P_D + T_B$

Junction Temperature estimation by measuring  $n^{\text{th}}$  Lead (Pin) Temperature (SO, DFN, etc.)

Junction Temperature estimation by measuring Board (Pad) Temperature (SO with Exposed Pad, DFN, etc.)

# **Thermal Parameters in Datasheet (NCV4269)**

Jmax

#### MAXIMUM RATINGS (T<sub>J</sub> = -40°C to 150°C)

| Parameter                                                             | Symbol                                 | Min                        | Max                      | Unit    |

|-----------------------------------------------------------------------|----------------------------------------|----------------------------|--------------------------|---------|

| Input to Regulator                                                    | VI<br>II                               | -40<br>Internally Limited  | 45<br>Internally Limited | V       |

| Input Transient to Regulator                                          | VI                                     | -                          | 60                       | V       |

| Sense Input                                                           | Vsi<br>Isi                             | -40<br>-1                  | 45<br>1                  | V<br>mA |

| Reset Threshold Adjust                                                | V <sub>RADJ</sub><br>I <sub>RADJ</sub> | -0.3<br>-10                | 7<br>10                  | V<br>mA |

| Reset Delay                                                           | V <sub>D</sub><br>I <sub>D</sub>       | –0.3<br>Internally Limited | 7<br>Internally Limited  | V       |

| Ground                                                                | l <sub>q</sub>                         | 50                         | -                        | mA      |

| Reset Output                                                          | V <sub>RO</sub><br>I <sub>RO</sub>     | -0.3<br>Internally Limited | 7<br>Internally Limited  | V       |

| Sense Output                                                          | V <sub>SO</sub><br>I <sub>SO</sub>     | –0.3<br>Internally Limited | 7<br>Internally Limited  | V       |

| Regulated Output                                                      | V <sub>Q</sub><br>I <sub>Q</sub>       | -0.5<br>-10                | 7.0<br>-                 | V<br>mA |

| Junction Temperature<br>Storage Temperature                           | T <sub>J</sub><br>T <sub>STG</sub>     | _<br>_50                   | 150<br>150               | °C<br>℃ |

| Input Voltage Operating Range<br>Junction Temperature Operating Range | V <sub>I</sub><br>T <sub>J</sub>       | _<br>_40                   | 45<br>150                | ∨<br>°C |

# **Thermal Parameters in Datasheet (NCV4269)**

$(A, (\Psi, (\Psi, (\Psi))))$

| Characteristic                                                             | Test Conditions (Typical V | alues) Unit |

|----------------------------------------------------------------------------|----------------------------|-------------|

| SO-8 Package (Note 5)                                                      |                            |             |

| Junction–to–Pin 4 ( $\Psi$ – JL4, $\Psi$ <sub>L4</sub> )                   | 53.8                       | °C/W        |

| Junction-to-Ambient Thermal Resistance ( $R_{\theta JA}$ , $\theta_{JA}$ ) | 170.9                      | °C/W        |

| SO–8 EP Package (Note 5)                                                   |                            |             |

| Junction–to–Pin 8 ( $\Psi$ – JL8, $\Psi_{L8}$ )                            | 23.7                       | °C/W        |

| Junction-to-Ambient Thermal Resistance (R $_{\theta JA}$ , $\theta_{JA}$ ) | 71.4                       | °C/W        |

| Junction-to-Pad ( $\Psi$ - JPad)                                           | 7.7                        | °C/W        |

| SO-14 Package (Note 5)                                                     |                            |             |

| Junction–to–Pin 4 ( $\Psi$ – JL4, $\Psi_{L4}$ )                            | 18.4                       | °C/W        |

| Junction–to–Ambient Thermal Resistance (R $_{	heta JA}$ , $\theta_{JA}$ )  | 111.6                      | °C/W        |

| SO–20 Package (Note 5)                                                     |                            |             |

| Junction–to–Pin 4 ( $\Psi$ – JL4, $\Psi$ L4)                               | 21.8                       | °C/W        |

| Junction–to–Ambient Thermal Resistance ( $R_{\theta JA}$ , $\theta_{JA}$ ) | 95.3                       | °C/W        |

<sup>5</sup> The θ and Ψ values are specified for particular application conditions (PCB parameters). Search in Application Section for other PCB parameters values, i.e. θ<sub>JA</sub> vs PCB area.

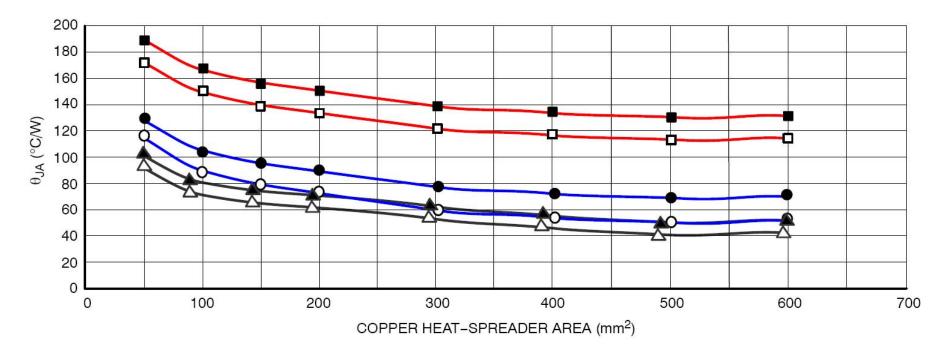

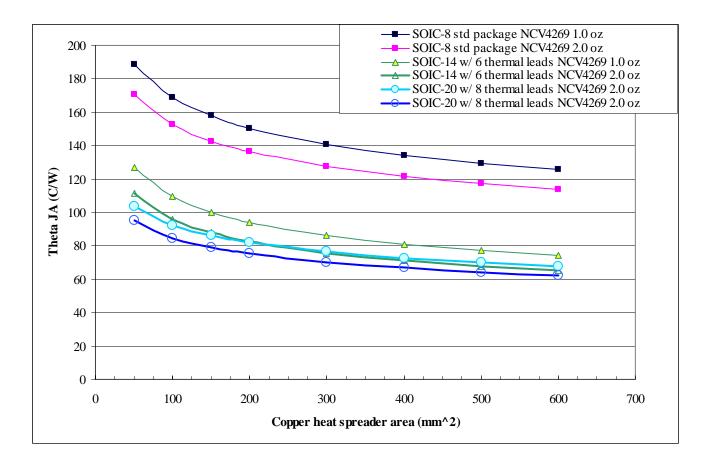

# Thermal Parameters in Datasheet (NCV4269) $\theta_{JA}$ vs PCB area

For given package the  $\theta_{\text{JA}}$  decreases:

- with increased PCB area

- with increased Cu thickness

SO-8 Std Package NCV4269, 1.0 oz

SO-8 Std Package NCV4269, 2.0 oz

SO-14 w/6 Thermal Leads NCV4269, 1.0 oz

SO-14 w/6 Thermal Leads NCV4269, 2.0 oz

SO-20 w/8 Thermal Leads NCV4269, 1.0 oz

SO-20 w/8 Thermal Leads NCV4269, 2.0 oz

# Suitable Packages for Good Thermal Performance

# **Selecting Suitable Package**

- There is no ideal option. There are always trade-offs among Thermal Performance, PCB footprint size and Cost.

- To choose package with sufficient thermal performance, consider mainly:

- Power dissipation (Steady state and pulsed)

- PCB parameters (Area, Cu thickness, Number of layers)

- Temperatures in particular points (Ambient, PCB)

- If the package cost is a key factor, try to consider:

- Eliminating other heat sources on PCB which will effectively increase temperature of the PCB

- Using multilayer PCBs larger copper areas and thicker Cu layers. Use thermal vias to improve PCB thermal performance

#### **LDO Packages Relative Performance Comparison**

|                                        |                     |               | _    |

|----------------------------------------|---------------------|---------------|------|

| Package Type                           | Thermal Performance | PCB footprint | Cost |

| D2PAK (3, 5, 7 leads + Tab)            | ++                  |               | -    |

| DPAK (3, 5 leads including Tab)        | ++                  | -             | -    |

| SOT-223 (3 leads + Tab)                | +                   | -             | +    |

| SO NB (8 leads)                        |                     | +             | ++   |

| SO NB Fused Leads (8 leads)            | -                   | +             | +    |

| SO EP (8 leads + Exposed Pad )         | +                   | +             |      |

| SO NB Fused Leads (14 leads)           | -                   | -             | +    |

| SO EP (16 leads + Exposed Pad)         | +                   |               |      |

| SO WB Fused Leads (16, 20 leads)       | -                   |               | -    |

| Micro8 (8 leads)                       |                     | ++            | +    |

| TSOP, SOT-23 (5, 6 leads)              |                     | ++            | ++   |

| DFN (6, 8, 10, 20 leads + Exposed Pad) | +                   | ++            | -    |

+ means relative advantage

- means relative disadvantage

NB - Narrow Body

WB – Wide Body

EP – Exposed Pad (At bottom side of package)

Fused Leads – Leads connected to the leadframe

# **Thermal Calculators for LDOs**

# Disclaimer

- These tools do not provide "guaranteed" results since real application conditions are different in most cases (i.e. PCB routing) and this factor has influence on results. There could also be other factors in real applications such as airflow, other heat sources, etc which affect the thermal behavior.

- These tools serve as a guide to show directions for proper thermal design. The models are limited for certain range of operating conditions (i.e. PCB area)

# **Thermal Calculator Important Facts**

- PCB Cu Area

- The area number units are mm<sup>2</sup>

- The larger is area the lower is thermal resistance

- PCB Cu Thickness

- The thickness units are oz (1 oz is 35  $\mu$ m, 2 oz is 70  $\mu$ m)

- The thicker is Cu layer the lower is thermal resistance

- The Single Layer PCB model is used

- Ambient Temperature, Power, Pulse With and Duty Cycle can be varied to see effect on Junction Temperature

- Results can be viewed for multiple packages if it is applicable for particular parts

# **Thermal Calculator Example (NCV4269)**

# **Thermal Calculator Results (NCV4269)**

# **Thermal Calculator File (NCV4269)**

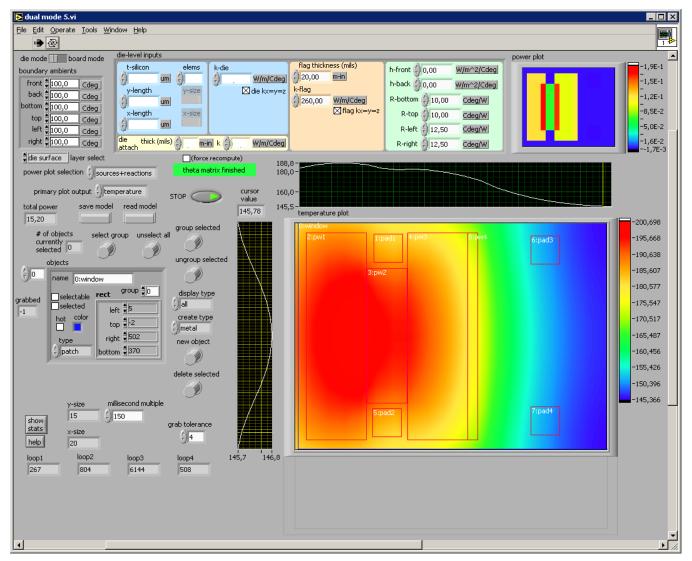

# Thermal Simulations used in Silicon Design Phase

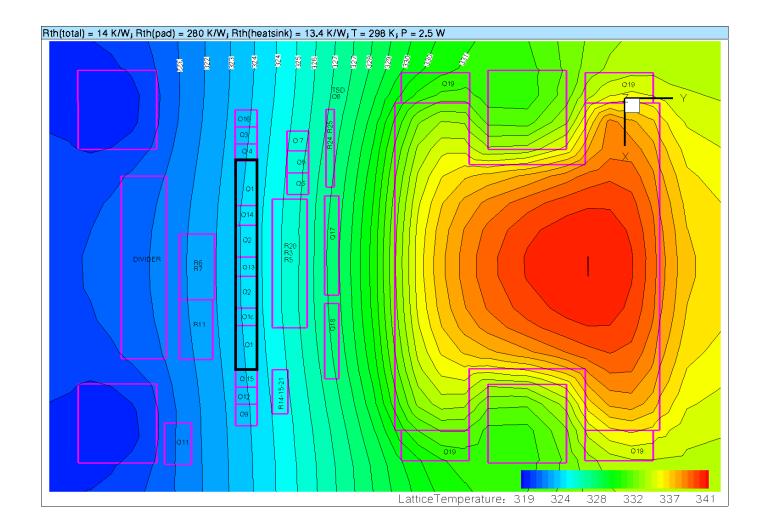

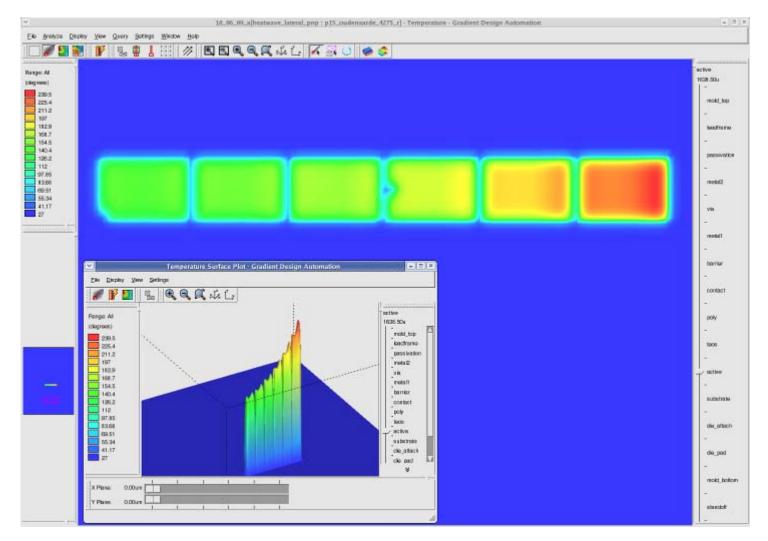

# **Thermal Simulation Tools at Silicon (Die) Level**

- The tools are important to predict thermal behavior of Silicon and provide guidelines for proper design and layout, mainly for temperature sensitive circuitries

- Three possible simulation tools in Silicon Design phase

- Thermal Tool

- Steady-state thermal simulations

- Three-layer die level simulation, linear system

- LabView environment

- Synopsys TCAD

- Steady-state as well as transient thermal simulations

- Nonlinear system, calculations based on the finite element method (FEM)

- HeatWave

- Steady-state, transient, thermal and electro-thermal simulations

- Nonlinear system, calculations based on the finite element method (FEM)

- The most precise and the most complex calculations

## **Thermal Tool**

ON

# Synopsys TCAD

### **HeatWave**

ON

# References

- Electronics System Thermal Design and Characterization (Presentation 8<sup>th</sup> July 2007), Roger Stout, P.E., ON Semiconductor

- Psi or Theta: Which One Should You Choose? (Article in Power Electronics Technology, May 2008), Roger Stout, P.E., ON Semiconductor

- 3. Application Note: AND8220/D How To Use Thermal Data Found in Data Sheets <u>http://www.onsemi.com/pub\_link/Collateral/AND8220-D.PDF</u>

- Thermal Simulations (Presentation 1<sup>st</sup> July 2009), Andrej Vrbicky, Bratislava Development Center, ON Semiconductor

- 5. Website <a href="http://www.jedec.org/">http://www.jedec.org/</a>

# **For More Information**

- View the extensive portfolio of power management products from ON Semiconductor at <u>www.onsemi.com</u>

- View reference designs, design notes, and other material supporting automotive applications at <u>www.onsemi.com/automotive</u>