IVC102

# PRECISION SWITCHED INTEGRATOR TRANSIMPEDANCE AMPLIFIER

## **APPLICATIONS**

- PRECISION LOW CURRENT MEASUREMENT

- PHOTODIODE MEASUREMENTS

- IONIZATION CHAMBER MEASUREMENTS

- CURRENT/CHARGE-OUTPUT SENSORS

- LEAKAGE CURRENT MEASUREMENT

## **FEATURES**

- ON-CHIP INTEGRATING CAPACITORS

- GAIN PROGRAMMED BY TIMING

- LOW INPUT BIAS CURRENT: 750fA max

- LOW NOISE

- LOW SWITCH CHARGE INJECTION

- FAST PULSE INTEGRATION

- LOW NONLINEARITY: 0.005% typ

- 14-PIN DIP, SO-14 SURFACE MOUNT

## DESCRIPTION

The IVC102 is a precision integrating amplifier with FET op amp, integrating capacitors, and low leakage FET switches. It integrates low-level input current for a user-determined period, storing the resulting voltage on the integrating capacitor. The output voltage can be held for accurate measurement. The IVC102 provides a precision, lower noise alternative to conventional transimpedance op amp circuits that require a very high value feedback resistor.

The IVC102 is ideal for amplifying low-level sensor currents from photodiodes and ionization chambers. The input signal current can be positive or negative.

TTL/CMOS-compatible timing inputs control the integration period, hold and reset functions to set the effective transimpedance gain and to reset (discharge) the integrator capacitor.

Package options include 14-Pin plastic DIP and SO-14 surface-mount packages. Both are specified for the -40°C to 85°C industrial temperature range.

# **SPECIFICATIONS**

At  $T_A = +25^{\circ}C$ ,  $V_S = \pm 15V$ ,  $R_L = 2k\Omega$ ,  $C_{INT} = C_1 + C_2 + C_3$ , 1ms integration period<sup>(1)</sup>, unless otherwise specified.

|                                                                                                                                                                                                               |                                                                                                                |                  | IVC102P, U                                                                                                            |                           |                                                        |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------------------------------------------|--|--|

| PARAMETER                                                                                                                                                                                                     | CONDITIONS                                                                                                     | MIN              | TYP                                                                                                                   | MAX                       | UNITS                                                  |  |  |

| TRANSFER FUNCTION<br>Gain Error<br>vs Temperature<br>Nonlinearity<br>Input Current Range<br>Offset Voltage <sup>(2)</sup><br>vs Temperature<br>vs Power Supply<br>Droop Rate, Hold Mode                       | $C_{INT} = C_1 + C_2 + C_3$ $V_0 = \pm 10V$ $I_{IN} = 0, C_{IN} = 50pF$ $V_S = +4.75/-10 \text{ to } +18/-18V$ | Ve               | $\begin{array}{c} = -(I_{ N})(T_{ NT})/C\\ \pm 5\\ \pm 25\\ \pm 0.005\\ \pm 100\\ -5\\ \pm 30\\ 150\\ -1 \end{array}$ | +25/–17<br>±20<br>750     | %<br>ppm/°C<br>%<br>μΑ<br>mV<br>μV/°C<br>μV/ν<br>nV/μs |  |  |

| OP AMP<br>Input Bias Current<br>vs Temperature<br>Offset Voltage (Op Amp V <sub>OS</sub> )<br>vs Temperature<br>vs Power Supply<br>Noise Voltage                                                              | S <sub>1</sub> , S <sub>2</sub> Open<br>V <sub>S</sub> = +4.75/-10 to +18/-18V<br>f = 1kHz                     | S                | -100<br>See Typical Cur<br>±0.5<br>±5<br>10<br>10                                                                     | ±750<br>ve<br>±5<br>100   | fA<br>mV<br>μV/°C<br>μV/V<br>nV/√Hz                    |  |  |

| INTEGRATION CAPACITORS<br>$C_1 + C_2 + C_3$<br>vs Temperature<br>$C_1$<br>$C_2$<br>$C_3$                                                                                                                      |                                                                                                                | 80               | 100<br>±25<br>10<br>30<br>60                                                                                          | 120                       | pF<br>ppm/°C<br>pF<br>pF<br>pF                         |  |  |

| OUTPUT<br>Voltage Range, Positive<br>Negative<br>Short-Circuit Current<br>Capacitive Load Drive<br>Noise Voltage                                                                                              | $R_{L} = 2k\Omega$ $R_{L} = 2k\Omega$                                                                          | (V+)-3<br>(V-)+3 | (V+)–1.3<br>(V–)+2.6<br>±20<br>500<br>See Typical Cur                                                                 | ve                        | V<br>V<br>mA<br>pF                                     |  |  |

| DYNAMIC CHARACTERISTIC<br>Op Amp Gain-Bandwidth<br>Op Amp Slew Rate<br>Reset<br>Slew Rate<br>Settling Time, 0.01%                                                                                             | 10V Step                                                                                                       |                  | 2<br>3<br>3<br>6                                                                                                      |                           | MHz<br>V/μs<br>V/μs<br>μs                              |  |  |

| $\begin{array}{c} \textbf{Digital inputs} \\ V_{\text{IH}} (referred to digital ground) \\ V_{\text{IL}} (referred to digital ground) \\ I_{\text{IH}} \\ I_{\text{IL}} \\ \text{Switching Time} \end{array}$ | $(TTL/CMOS Compatible) \\ (Logic High) \\ (Logic Low) \\ V_{IH} = 5V \\ V_{IL} = 0V$                           | 2<br>0.5         | 2<br>0<br>100                                                                                                         | 5.5<br>0.8                | V<br>V<br>μA<br>μA<br>ns                               |  |  |

| POWER SUPPLY<br>Voltage Range: Positive<br>Negative<br>Current: Positive<br>Negative<br>Analog Ground<br>Digital Ground                                                                                       |                                                                                                                | +4.75<br>–10     | +15<br>-15<br>4.1<br>-1.6<br>-0.2<br>-2.3                                                                             | +18<br>-18<br>5.5<br>-2.2 | V<br>V<br>mA<br>mA<br>mA                               |  |  |

| TEMPERATURE RANGE         Operating Range         Storage         Thermal Resistance, $\theta_{JA}$ DIP         SO-14                                                                                         |                                                                                                                | -40<br>-55       | 100<br>150                                                                                                            | 85<br>125                 | °C<br>°C<br>°C/W<br>°C/W                               |  |  |

NOTES: (1) Standard test timing: 1ms integration, 200µs hold, 100µs reset. (2) Hold mode output voltage after 1ms integration of zero input current. Includes op amp offset voltage, integration of input error current and switch charge injection effects.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

### ABSOLUTE MAXIMUM RATINGS

| Supply Voltage, V+ to V           |                 |

|-----------------------------------|-----------------|

| Logic Input Voltage               | V– to V+        |

| Output Short Circuit to Ground    | Continuous      |

| Operating Temperature             | 40°C to +125°C  |

| Storage Temperature               | –55°C to +125°C |

| Lead Temperature (soldering, 10s) | 300°C           |

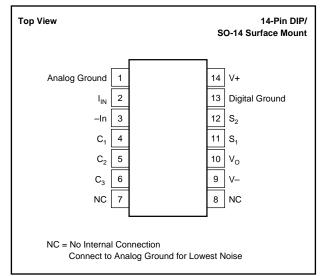

#### **PIN CONNECTIONS**

#### PACKAGE INFORMATION

| PRODUCT | PACKAGE             | PACKAGE DRAWING<br>NUMBER <sup>(1)</sup> |

|---------|---------------------|------------------------------------------|

| IVC102P | 14-Pin DIP          | 010                                      |

| IVC102U | SO-14 Surface Mount | 235                                      |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix D of Burr-Brown IC Data Book.

# ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Burr-Brown recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

# **TYPICAL PERFORMANCE CURVES**

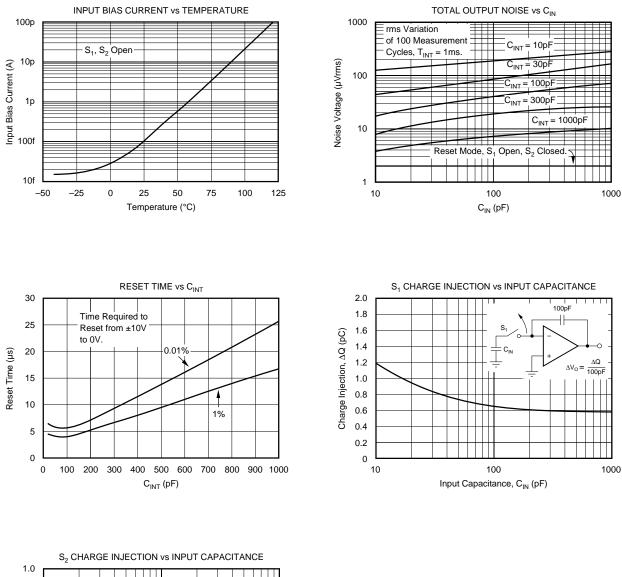

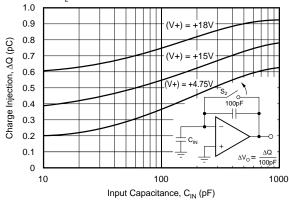

At  $T_A = +25^{\circ}C$ ,  $V_S = \pm 15V$ ,  $R_L = 2k\Omega$ ,  $C_{INT} = C_1 + C_2 + C_3$ , 1ms integration period, unless otherwise specified.

## **APPLICATION INFORMATION**

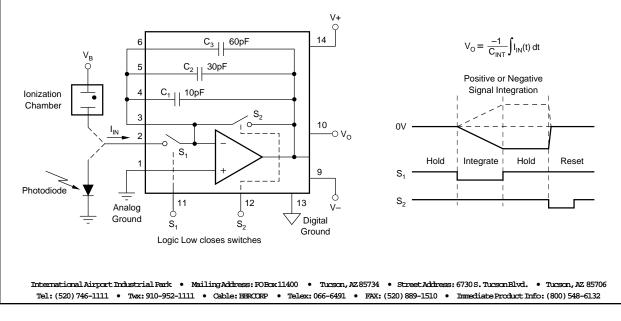

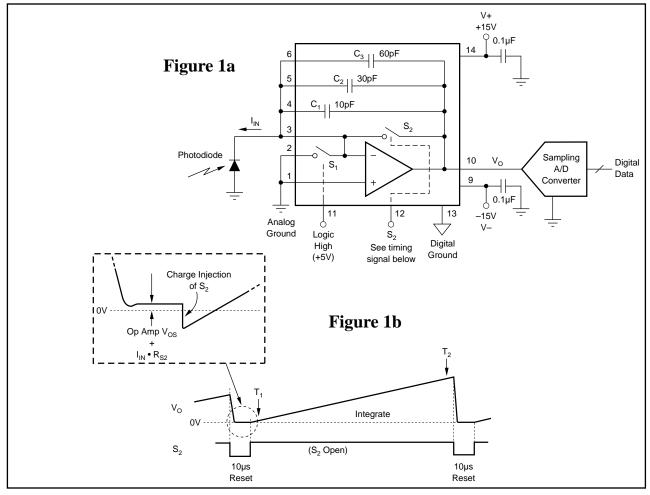

Figure 1 shows the basic circuit connections to operate the IVC102. Bypass capacitors are shown connected to the power supply pins. Noisy power supplies should be avoided or decoupled and carefully bypassed.

The Analog Ground terminal, pin 1, is shown internally connected to the non-inverting input of the op amp. This terminal connects to other internal circuitry and should be connected to ground. Approximately 200µA flows out of this terminal.

Digital Ground, pin 13, should be at the same voltage potential as analog ground (within 100mV). Analog and Digital grounds should be connected at some point in the system, usually at the power supply connections to the circuit board. A separate Digital Ground is provided so that noisy logic signals can be referenced to separate circuit board traces.

Integrator capacitors  $C_1$ ,  $C_2$  and  $C_3$  are shown connected in parallel for a total  $C_{INT} = 100 \text{pF}$ . The IVC102 can be used for a wide variety of integrating current measurements. The input signal connections and control timing and  $C_{INT}$  value will depend on the sensor or signal type and other application details.

#### **BASIC RESET-AND-INTEGRATE MEASUREMENT**

Figure 1 shows the circuit and timing for a simple reset-andintegrate measurement. The input current is connected directly to the inverting input of the IVC102, pin 3. Input current is shown flowing out of pin 3, which produces a positive-going ramp at  $V_O$ . Current flowing into pin 3 would produce a negative-going ramp.

A measurement cycle starts by resetting the integrator output voltage to 0V by closing S<sub>2</sub> for 10 $\mu$ s. Integration of the input current begins when S<sub>2</sub> opens and the input current begins to charge C<sub>INT</sub>. V<sub>O</sub> is measured with a sampling a/d converter at the end of an integration period, just prior to the next reset period. The ideal result is proportional to the average input current (or total accumulated charge).

Switch  $S_2$  is again closed to reset the integrator output to 0V before the next integration period.

This simple measurement arrangement is suited to many applications. There are, however, limitations to this basic approach. Input current continues to flow through  $S_2$  during the reset period. This leaves a small voltage on  $C_{INT}$  equal to the input current times  $R_{S2}$ , the on-resistance of  $S_2$ , approximately  $1.5 \mathrm{k}\Omega$ .

FIGURE 1. Reset-and Integrate Connections and Timing.

In addition, the offset voltage of the internal op amp and charge injection of  $S_2$  contribute to the voltage on  $C_{INT}$  at the start of integration.

Performance of this basic approach can be improved by sampling  $V_0$  after the reset period at  $T_1$  and subtracting this

measurement from the final sample at  $T_2$ . Op amp offset voltage, charge injection effects and  $I \cdot R_{S2}$  offset voltage on  $S_2$  are removed with this two-point measurement. The effective integration period is the time between the two measurements,  $T_2 \cdot T_1$ .

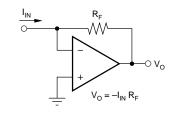

### COMPARISON TO CONVENTIONAL TRANSIMPEDANCE AMPLIFIERS

With the conventional transimpedance amplifier circuit of Figure 2a, input current flows through the feedback resistor,  $R_F$ , to create a proportional output voltage.

$$V_{O} = -I_{IN} R_{F}$$

The transimpedance gain is determined by  $R_F$ . Very large values of  $R_F$  are required to measure very small signal current. Feedback resistor values exceeding 100M $\Omega$  are common.

The IVC102 (Figure 2b) provides a similar function, converting an input current to an output voltage. The input current flows through the feedback capacitor,  $C_{INT}$ , charging it at a rate that is proportional to the input current. With a constant input current, the IVC102's output voltage is

$$V_0 = -I_{IN} T_{INT} / C_{INT}$$

after an integration time of T<sub>INT</sub>.

#### Conventional Transimpedance Amplifier Figure 2a

Provides time-continuous output voltage proportional to  ${\rm I}_{\rm IN}$

$V_O$  is proportional to the integration time,  $T_{INT}$ , and inversely proportional to the feedback capacitor,  $C_{INT}$ . The effective transimpedance gain is  $T_{INT}/C_{INT}$ . Extremely high gain that would be impractical to achieve with a conventional transimpedance amplifier can be achieved with small integration capacitor values and/or long integration times. For example the IVC102 with  $C_{INT} = 100$ pF and  $T_{INT} = 100$ ms provides an effective transimpedance of 1G $\Omega$ . A 10nA input current would produce a 10V output after 100ms integration.

The integrating behavior of the IVC102 reduces noise by averaging the input noise of the sensor, amplifier, and external sources.

#### Integrating Transimpedance Amplifier Figure 2b

for constant  $I_{IN}$ , at the end of  $T_{INT}$

$$V_{O} = -I_{IN} \frac{T_{INT}}{C_{INT}}$$

Output voltage after integration period is proportional to average  ${\rm I}_{\rm IN}$  throughout the period.

FIGURE 2. Comparison to a Conventional Transimpedance Amplifier.

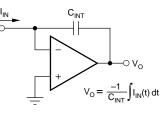

#### **CURRENT-OUTPUT SENSORS**

Figure 3 shows a model for many current-output sensors such as photodiodes and ionization chambers. Sensor output is a signal-dependent current with a very high source resistance. The output is generally loaded into a low impedance so that the terminal voltage is kept very low. Typical sensor capacitance values range from 10pF to over 100pF. This capacitance plays a key role in operation of the switched-input measurement technique (see next section).

FIGURE 3. Switched-Input Measurement Technique.

#### SWITCHED-INPUT MEASUREMENT TECHNIQUE

While the basic reset-and-integrate measurement arrangement in Figure 1 is satisfactory for many applications, the switched-input timing technique shown in Figure 3 has important advantages. This method can provide continuous integration of the input signal. Furthermore, it can hold the output voltage constant after integration for stable conversion (desirable for a/d converter without a sample/hold). Input connections and timing are shown in Figure 3.

The timing diagram, Figure 3b, shows that  $S_1$  is closed only when  $S_2$  is open. During the short period that  $S_1$  is open (30µs in this timing example), any signal current produced by the sensor will charge the sensor's source capacitance. This charge is then transferred to  $C_{INT}$  when  $S_1$  is closed. As a result, no charge produced by the sensor is lost and the input signal is continuously integrated. Even fast input pulses are accurately integrated.

The input current,  $I_{IN}$ , is shown as a conventional current flowing into pin 2 in this diagram but the input current could be bipolar (positive or negative). Current flowing out of pin 2 would produce a positive-ramping  $V_{O}$ .

The timing sequence proceeds as follows:

#### **Reset Period**

The integrator is reset by closing switch  $S_2$  with  $S_1$  open. A 10 $\mu$ s reset time is recommended to allow the op amp to slew to 0V and settle to its final value.

#### **Pre-Integration Hold**

$S_2$  is opened, holding  $V_O$  constant for 10µs prior to integration. This pre-integration hold period assures that  $S_2$  is fully open before  $S_1$  is closed so that no input signal is lost. A minimum of 1µs is recommended to avoid switching overlap. The 10µs hold period shown in Figure 3b also allows an a/d converter measurement to be made at point A. The purpose of this measurement at A is discussed in the "Offset Errors" section.

#### Integration on CINT

Integration of the input current on  $C_{INT}$  begins when  $S_1$  is closed. An immediate step output voltage change occurs as the charge that was stored on the input sensor capacitance is transferred to  $C_{INT}$ . Although this period of charging  $C_{INT}$  occurs only while  $S_1$  is closed, the charge transferred as  $S_1$  is closed causes the *effective* integration time to be equal to the complete conversion period—see Figure 3b.

The integration period could range from 100 $\mu$ s to many minutes, depending on the input current and C<sub>INT</sub> value. While S<sub>1</sub> is closed, I<sub>IN</sub> charges C<sub>INT</sub>, producing a negative-going ramp at the integrator output voltage, V<sub>0</sub>. The output voltage at the end of integration is proportional to the average input current throughout the complete conversion cycle, including the integration period, reset and both hold periods.

#### **Hold Period**

Opening  $S_1$  halts integration on  $C_{INT}$ . Approximately 5µs after  $S_1$  is opened, the output voltage is stable and can be measured (at point B). The hold period is 10µs in this example.  $C_{INT}$  remains charged until a  $S_2$  is again closed, to reset for the next conversion cycle.

In this timing example,  $S_1$  is open for a total of 30µs. During this time, signal current from the sensor charges the sensor source capacitance. Care should be used to assure that the voltage developed on the sensor does not exceed approximately 200mV during this time. The  $I_{IN}$  terminal, pin 2, is internally clamped with diodes. If these diodes forward bias, signal current will flow to ground and will not be accurately integrated.

A maximum of 333nA signal current could be accurately integrated on a 50pF sensor capacitance for  $30\mu s$  before 200mV would be developed on the sensor.

$$I_{MAX} = (50 \text{pF}) (200 \text{mV}) / 30 \mu \text{s} = 333 \text{nA}$$

#### **OFFSET ERRORS**

Figure 3c shows the effect on  $V_O$  due to op amp input offset voltage, input bias current and switch charge injection. It assumes zero input current from the sensor. The various offsets and charge injection ( $\Delta Q$ ) jumps shown are typical of that seen with a 50pF source capacitance. The specified "transfer function offset voltage" is the voltage measured during the hold period at B. Transfer function offset voltage is dominated by the charge injection of S<sub>2</sub> opening and op amp V<sub>OS</sub>. The opening and closing charge injections of S<sub>1</sub> are very nearly equal and opposite and are not significant contributors.

Note that using a two-point difference measurement at A and B can dramatically reduce offset due to op amp  $V_{OS}$  and  $S_2$  charge injection. The remaining offset with this B-A measurement is due to op amp input bias current charging  $C_{INT}$ . This error is usually very small and is exaggerated in the figure.

#### **DIGITAL SWITCH INPUTS**

The digital control inputs to  $S_1$  and  $S_2$  are compatible with standard CMOS or TTL logic. Logic input pins 11 and 12 are high impedance and the threshold is approximately 1.4V relative to Digital Ground, pin 13. A logic "low" closes the switch.

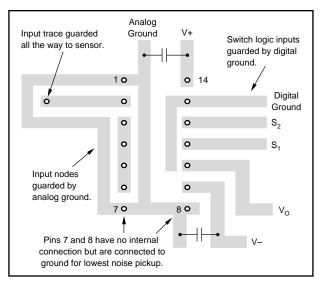

Use care in routing these logic signals to their respective input pins. Capacitive coupling of logic transitions to sensitive input nodes (pins 2 through 6) and to the positive power supply (pin 14) will dramatically increase charge injection and produce errors. Route these circuit board traces over a ground plane (digital ground) and route digital ground traces between logic traces and other critical traces for lowest charge injection. See Figure 4.

5V logic levels are generally satisfactory. Lower voltage logic levels may help reduce charge injection errors, depending on circuit layout. Logic high voltages greater than 5.5V, or higher than the V+ supply are not recommended.

FIGURE 4. Circuit Board Layout Techniques.

#### INPUT BIAS CURRENT ERRORS

Careful circuit board layout and assembly techniques are required to achieve the very low input bias current capability of the IVC102. The critical input connections are at ground potential, so analog ground should be used as a circuit board guard trace surrounding all critical nodes. These include pins 2, 3, 4, 5 and 6. See Figure 4.

Input bias current increases with temperature—see typical performance curve Input Bias Current vs Temperature.

#### HOLD MODE DROOP

Hold-mode droop is a slow change in output voltage primarily due to op amp input bias current. Droop is specified using the internal  $C_{INT} = 100$ pF and is based on a -100fA typical input bias current. Current flows out of the inverting input of the internal op amp.

Droop Rate =

$$\frac{-100 \text{fA}}{\text{C}_{\text{INT}}}$$

With  $C_{INT} = 100 pF$ , the droop rate is typically only  $1 nV/\mu s$ —slow enough that it rarely contributes significant error at moderate temperatures.

Since the input bias current increases with temperature, the droop rate will also increase with temperature. The droop rate will approximately double for each 10°C increase in junction temperature—see typical curves.

Droop rate is inversely proportional to  $C_{INT}$ . If an external integrator capacitor is used, a low leakage capacitor should be selected to preserve the low droop performance of the IVC102.

#### INPUT CURRENT RANGE

Extremely low input currents can be measured by integrating for long periods and/or using a small value for  $C_{INT}$ . Input bias current of the internal op amp is the primary source of error.

Larger input currents can be measured by increasing the value of  $C_{INT}$  and/or using a shorter integration time. Input currents greater than 200µA should not be applied to the pin 2 input, however. The approximately  $1.5k\Omega$  series resistance of S<sub>1</sub> will create an input voltage at pin 2 that will begin to forward-bias internal protection clamp diodes. Any current that flows through these protection diodes will not be accurately integrated. See "Input Impedance" section for more information on input current-induced voltage.

Input current greater than 200 $\mu$ A can, however, be connected directly to pin 3, using the simple reset-integrate technique shown in Figure 1. Current applied at this input can be externally switched to avoid excessive I•R voltage across S<sub>2</sub> during reset. Inputs up to 5mA at pin 3 can be accurately integrated if C<sub>INT</sub> is made large enough to limit slew rate to less than 1V/ $\mu$ s. A 5mA input current would require C<sub>INT</sub> = 5nF to produce a 1V/ $\mu$ s slew rate. The input current appears as load current to the internal op amp, reducing its ability to drive an external load.

#### CHOOSING CINT

Internal capacitors C<sub>1</sub>, C<sub>2</sub> and C<sub>3</sub> are high quality metal/ oxide types with low leakage and excellent dielectric characteristics. Temperature stability is excellent—see typical curve. They can be connected for C<sub>INT</sub> = 10pF, 30pF, 40pF, 60pF, 70pF, 90pF or 100pF. Connect unused internal capacitor pins to analog ground. Accuracy is  $\pm 20\%$ , which directly influences the gain of the transfer function.

A larger value external  $C_{INT}$  can be connected between pins 3 and 10 for slower/longer integration. Select a capacitor type with low leakage and good temperature stability. Teflon<sup>®</sup>, polystyrene or polypropylene capacitors generally provide excellent leakage, temperature drift and voltage coefficient characteristics. Lower cost types such as NPO ceramic, mica or glass may be adequate for many applications. Larger values for  $C_{INT}$  require a longer reset time—see typical curves.

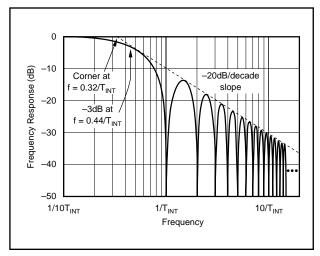

#### FREQUENCY RESPONSE

Integration of the input signal for a fixed period produces a deep null (zero response) at the frequency  $1/T_{\rm INT}$  and its harmonics. An ac input current at this frequency (or its harmonics) has zero average value and therefore produces no output. This property can be used to position response nulls at critical frequencies. For example, a 16.67ms integration period produces response nulls at 60Hz, 120Hz, 180Hz, etc., which will reject ac line frequency noise and its harmonics. Response nulls can be positioned to reduce interference from system clocks or other periodic noise.

Response to all frequencies above  $f = 1/T_{INT}$  falls at -20dB/decade. The effective corner frequency of this single-pole response is approximately  $1/2.8T_{INT}$ .

For the simple reset-and-integrate measurement technique,  $T_{INT}$  is equal to the to the time that  $S_2$  is open. The switchedinput technique, however, effectively integrates the input signal throughout the full measurement cycle, including the reset period and both hold periods. Using the timing shown in Figure 3, the *effective* integration time is 1/Ts, where Ts is the repetition rate of the sampling.

#### **INPUT IMPEDANCE**

The input impedance of a perfect transimpedance circuit is zero ohms. The input voltage ideally would be zero for any input current. The actual input voltage when directly driving the integrator input (pin 3) is proportional to the output slew rate of the integrator. A  $1V/\mu s$  slew rate produces approximately 100mV at pin 3. The input of the integrator can be modeled as a resistance:

$$R_{\rm IN} = 10^{-7} / C_{\rm INT}$$

(2)

with  $R_{IN}$  in  $\Omega$  and  $C_{INT}$  in Farads.

Using the internal

$$C_{INT} = C_1 + C_2 + C_3 = 100 pF$$

(3)

$R_{IN} = 10^{-7}/100 pF = 1 k\Omega$

Teflon® E. I. Du Pont de Nemours & Co.

FIGURE 5. Frequency Response of Integrating Converter.

The input resistance seen at pin 2 includes an additional  $1.5k\Omega$ , the on-resistance of S<sub>1</sub>. The total input resistance is the sum of the switch resistance and R<sub>IN</sub>, or  $2.5k\Omega$  in this example.

Slew rate limit of the internal op amp is approximately  $3V/\mu s$ . For most applications, the slew rate of  $V_{OUT}$  should be limited to  $1V/\mu s$  or less. The rate of change is proportional to  $I_{IN}$  and inversely proportional to  $C_{INT}$ :

Slew Rate =

$$\frac{I_{IN}}{C_{INT}}$$

This can be important in some applications since the slewinduced input voltage is applied to the sensor or signal source. The slew-induced input voltage can be reduced by increasing  $C_{INT}$ , which reduces the output slew rate.

#### NONLINEARITY

Careful nonlinearity measurements of the IVC102 yield typical results of approximately  $\pm 0.005\%$  using the internal input capacitors (C<sub>INT</sub> = 100pF). Nonlinearity will be degraded by using an external integrator capacitor with poor voltage coefficient. Performance with the internal capacitors is typically equal or better than the sensors it is used to measure. Actual application circuits with sensors such as a photodiode may have other sources of nonlinearity.

### PACKAGING INFORMATION

| Orderable Device | Status   | Package Type | •       |    | Package Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Top-Side Markings | Samples |

|------------------|----------|--------------|---------|----|-------------|----------------------------|------------------|---------------------|--------------|-------------------|---------|

|                  | (1)      |              | Drawing |    |             | (2)                        |                  | (3)                 |              | (4)               |         |

| IVC102P          | OBSOLETE | E PDIP       | Ν       | 14 |             | TBD                        | Call TI          | Call TI             |              |                   |         |

| IVC102U          | ACTIVE   | SOIC         | D       | 14 | 50          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-3-260C-168 HR |              | IVC102U           | Samples |

| IVC102U/2K5      | ACTIVE   | SOIC         | D       | 14 | 2500        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-3-260C-168 HR |              | IVC102U           | Samples |

| IVC102U/2K5G4    | ACTIVE   | SOIC         | D       | 14 | 2500        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-3-260C-168 HR |              | IVC102U           | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between

the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above. Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> Only one of markings shown within the brackets will appear on the physical device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## PACKAGE MATERIALS INFORMATION

www.ti.com

Texas Instruments

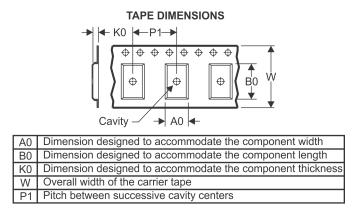

### TAPE AND REEL INFORMATION

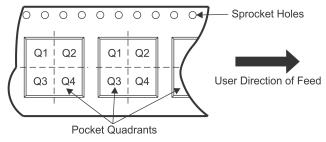

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All | dimensions are nominal |  |

|------|------------------------|--|

|      |                        |  |

|      |                        |  |

| Device      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| IVC102U/2K5 | SOIC            | D                  | 14 | 2500 | 330.0                    | 16.4                     | 6.5        | 9.0        | 2.1        | 8.0        | 16.0      | Q1               |

TEXAS INSTRUMENTS

www.ti.com

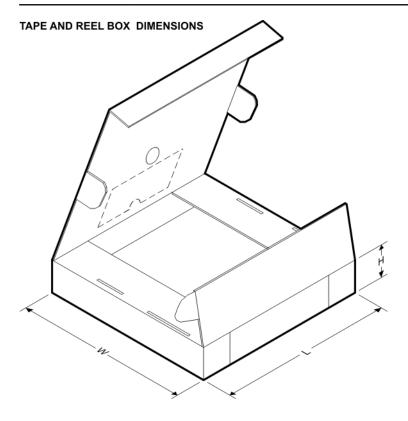

## PACKAGE MATERIALS INFORMATION

24-Jul-2013

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| IVC102U/2K5 | SOIC         | D               | 14   | 2500 | 367.0       | 367.0      | 38.0        |

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ectivity                      |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated